在FPGA图像处理领域,VGA(Video Graphics Array)接口作为一种经典的视频传输标准,因其成本低、结构简单、应用灵活而广泛应用。本文将深入探讨FPGA中VGA接口的工作原理、时序参数以及相关的实现方法,为FPGA图像处理实战提供详尽的技术指导。

一、VGA接口概述

VGA接口,全称为Video Graphics Array,是IBM公司在1987年推出的一种使用模拟信号的视频传输标准。该接口通过传输红、绿、蓝三原色信号以及行同步(HSYNC)和场同步(VSYNC)信号,实现视频图像的显示。VGA接口具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛应用。

二、VGA接口工作原理

VGA接口的工作原理基于逐行扫描技术。电子束从屏幕的左上角开始,从左向右逐行扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,同时CRT(阴极射线管)对电子束进行消隐。当扫描完所有的行,形成一帧图像后,用场同步信号进行场同步,并使扫描回到屏幕左上方,开始下一帧的扫描。

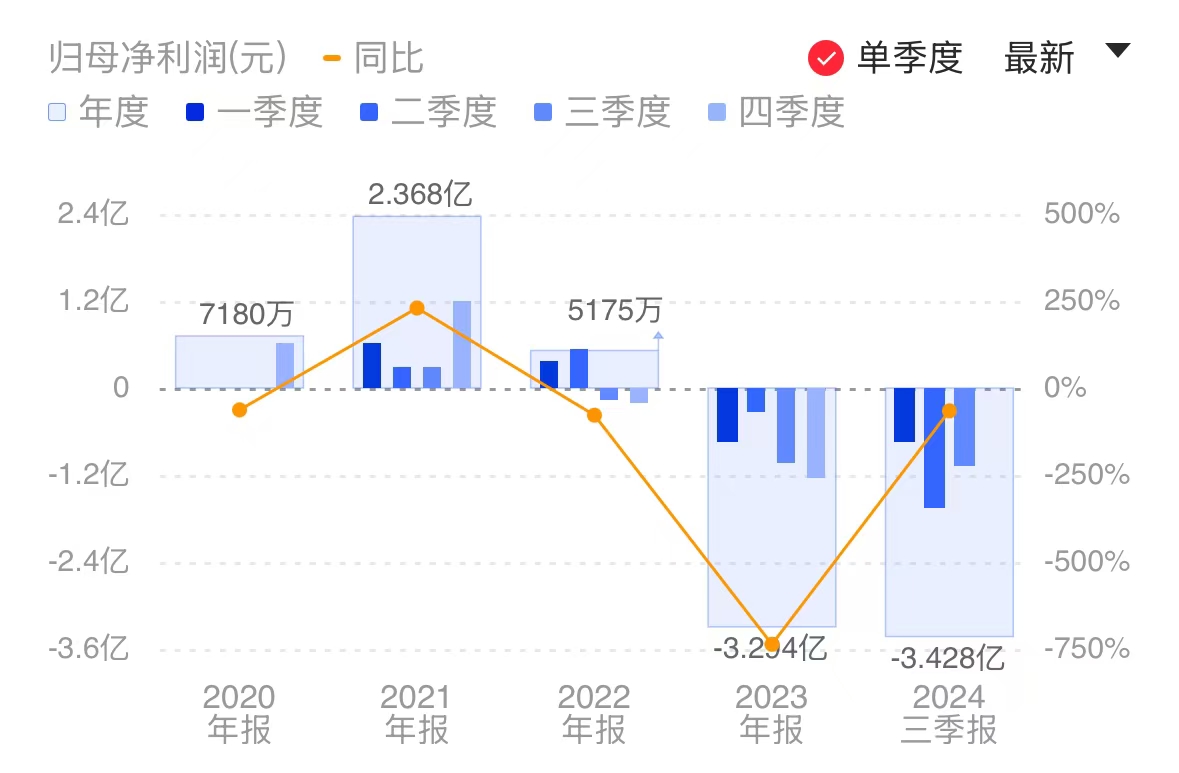

三、VGA时序参数

VGA时序包含行时序和场时序两部分,它们是控制图像显示的关键参数。

1. 行时序参数

行同步(HSYNC):用于每行扫描的同步信号,保持低电平一段时间,其余时间保持高电平。

行消隐(Hor Back Porch):行同步信号之后的消隐区域,不显示图像数据。

行视频有效(Hor Active Video):实际显示图像数据的区域。

行前肩(Hor Front Porch):行视频有效区域之前的过渡区域。

一行总像素数(H_TOTAL)由这四个部分组成:H_TOTAL = H_SYNC + H_BACK + H_ACTIVE + H_FRONT。

2. 场时序参数

场同步(VSYNC):用于每帧扫描的同步信号,与行同步类似,保持低电平一段时间,其余时间保持高电平。

场消隐(Ver Back Porch):场同步信号之后的消隐区域,不显示图像数据。

场视频有效(Ver Active Video):实际显示图像帧的区域。

场前肩(Ver Front Porch):场视频有效区域之前的过渡区域。

一场总行数(V_TOTAL)同样由这四个部分组成:V_TOTAL = V_SYNC + V_BACK + V_ACTIVE + V_FRONT。

四、FPGA实现VGA接口

在FPGA中实现VGA接口,需要精确控制时序信号的生成和图像数据的输出。以下是一个简化的实现步骤:

时钟分频:根据所需的分辨率和刷新率,通过PLL(锁相环)或分频器生成像素时钟。

时序控制:根据VGA时序参数,编写逻辑控制行同步信号和场同步信号的生成。这通常涉及计数器的使用,以跟踪当前扫描的行数和像素数。

图像数据处理:在像素时钟的驱动下,根据当前扫描的位置,从图像缓冲区中读取相应的图像数据,并输出到VGA接口。

数模转换:由于VGA接口传输的是模拟信号,因此需要将FPGA输出的数字图像数据转换为模拟信号。这可以通过专用的视频转换芯片(如ADV7123)实现,或者通过电阻匹配网络进行简单的数模转换。

五、示例代码

以下是一个简化的VGA接口控制模块的代码示例(使用Verilog语言):

verilog

module vga_controller(

input clk,

input rst_n,

output reg vga_hsync,

output reg vga_vsync,

// 其他输出信号...

);

parameter H_SYNC = 10'd96;

parameter H_BACK = 10'd48;

parameter H_ACTIVE = 10'd640;

parameter H_FRONT = 10'd16;

parameter H_TOTAL = H_SYNC + H_BACK + H_ACTIVE + H_FRONT;

parameter V_SYNC = 10'd2;

parameter V_BACK = 10'd33;

parameter V_ACTIVE = 10'd480;

parameter V_FRONT = 10'd10;

parameter V_TOTAL = V_SYNC + V_BACK + V_ACTIVE + V_FRONT;

reg [11:0] x_cnt = 0;

reg [11:0] y_cnt = 0;