在当前的半导体产业环境下,中国IC设计和整个半导体产业链面临着复杂的挑战与机遇。从宏观来看,全球半导体行业正在经历不均衡的复苏,AI应用作为主要推动力,持续推动技术创新和市场需求增长。然而,国内市场虽然需求仍在,但受限于不断加剧的外部封锁和技术限制,芯片制造的生产不得不在不同晶圆厂之间调整和迁移。尽管这一变化带来了不小的挑战,但它也为国产芯片全产业链的塑造和创新提供了独特的机遇。

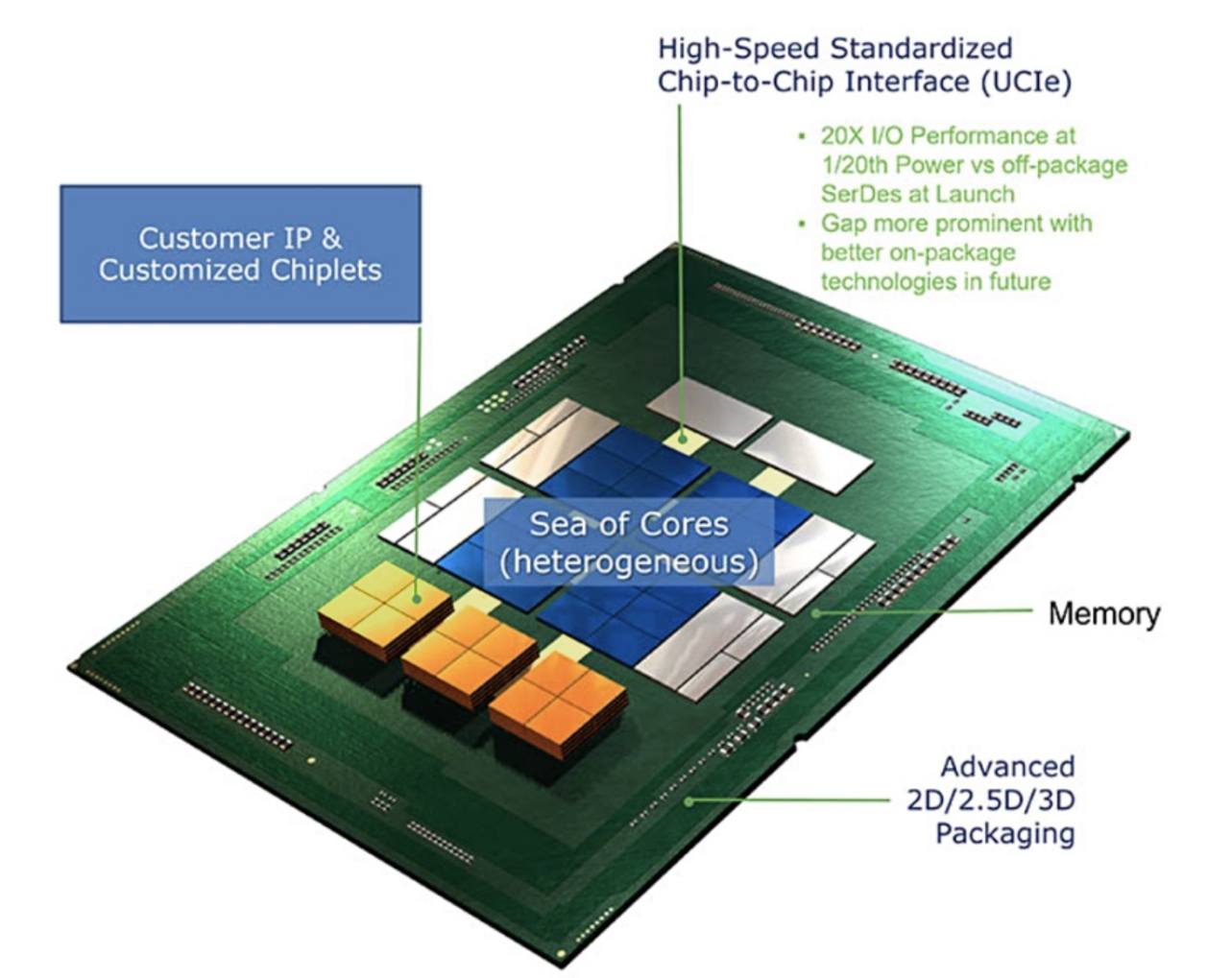

在这种背景下,Chiplet技术和相关的互连IP变得尤为重要。作为解决制程瓶颈、提升性能和灵活性的有效手段,Chiplet技术不仅为国内半导体企业提供了突破传统单片设计的机会,也在芯片产业自主可控的过程中扮演了重要角色。互连IP,作为Chiplet架构的核心组件之一,正是实现不同模块之间高效通信的关键,为系统集成和功能扩展提供了强大支持。

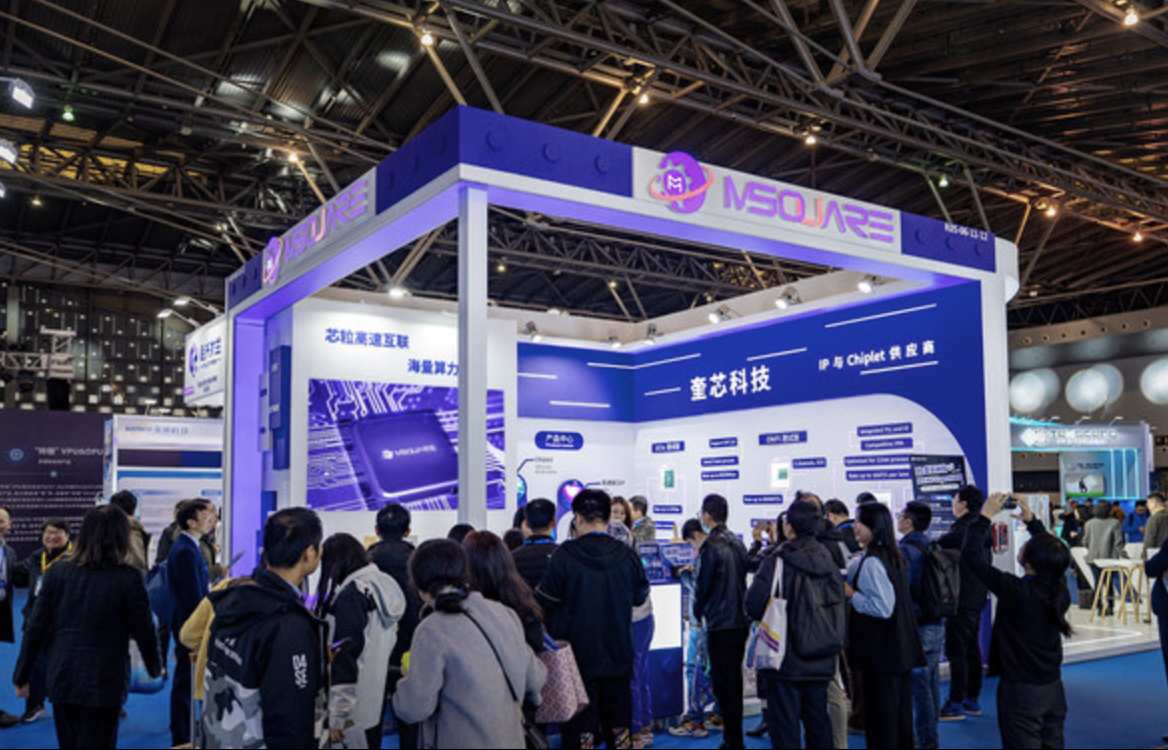

在这一过程中,奎芯科技作为国内半导体互连IP领域的先锋企业,积极推动Chiplet技术的发展和应用。在最近ICCAD-Expo上,我们有幸采访到了奎芯科技联合创始人兼副总裁唐睿博士,他分享了奎芯科技的M2LINK技术的独特价值,以及对于中国芯片设计产业的展望。

ML100 IO Die:创新的“分离”设计,带来三大价值

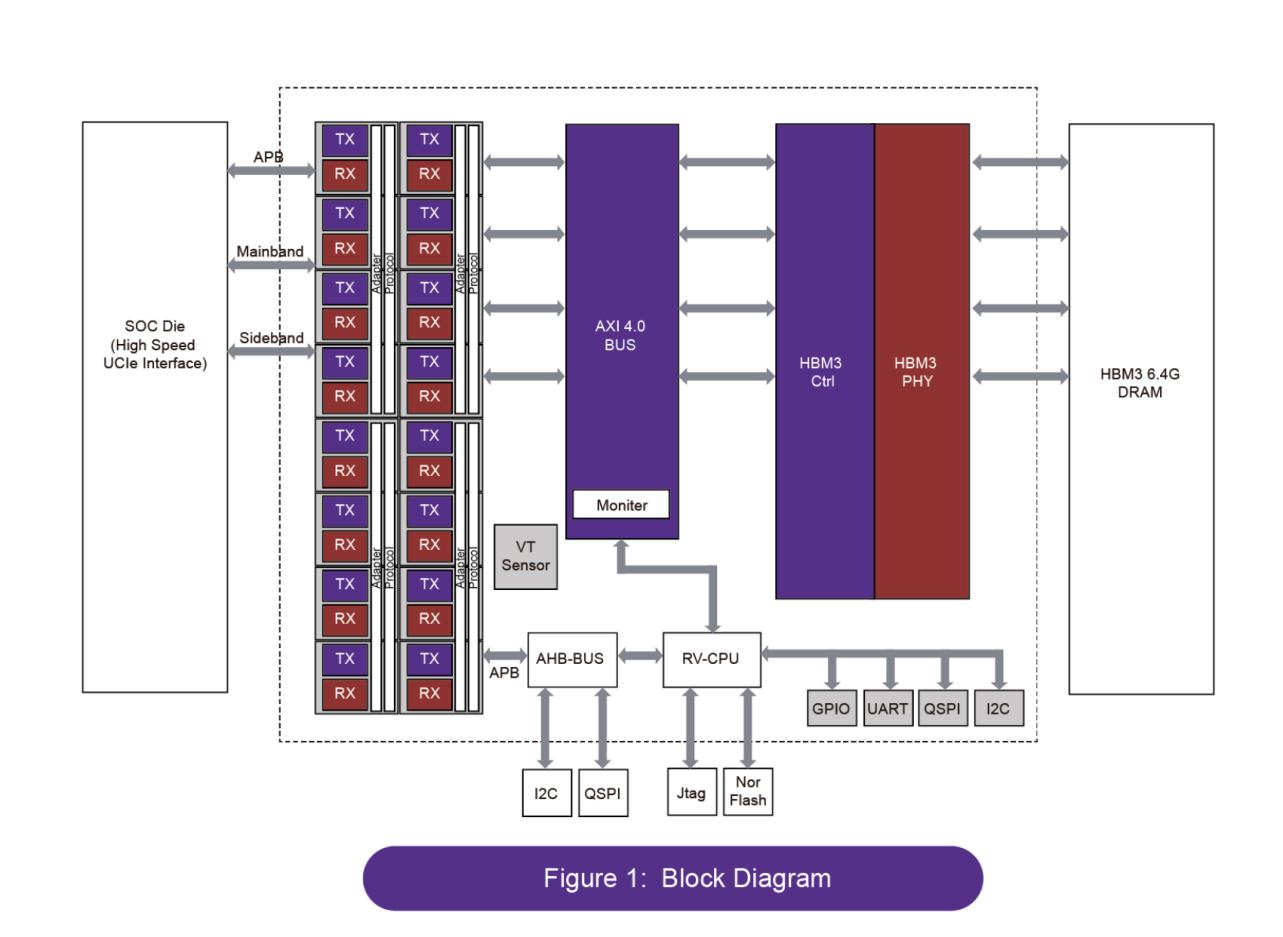

ML100 IO Die是MSquare推出的一款集成了高带宽内存(HBM3)和UCIe(Die-to-Die)互连IP的IO Die。它支持单模块配置下高达1 TB/s的传输带宽,符合UCIe 1.1规范,能够实现低延迟和高速的数据传输。这一创新产品发挥了奎芯科技M2LINK关键技术优势——它解决了UCIe接口和HBM内存之间的连接问题,提升内存的连接效率和带宽。

在高性能计算中,内存带宽和计算节点之间的连接至关重要,UCIe(Universal Chiplet Interconnect Express)标准是一种新兴的接口标准,旨在增强芯片模块之间的连接性,尤其适用于Chiplet架构。

【接口带宽匹配,效能和成本兼得】

唐睿提到,UCIe接口的速率是32Gbps,而他们目前的设计包含了16个模组。这个接口的带宽与HBM3内存接口的带宽正好匹配。HBM3是最新的高带宽内存技术,相比传统内存,它能提供更高的数据传输速率,因此在与UCIe的接口设计中,奎芯科技的IP设计能够有效匹配,保证系统性能。

通过UCIe接口与HBM3内存带宽的匹配,奎芯科技的设计能够实现非常高效的性能,同时降低了封装成本。因为在传统的芯片设计中,封装和连接带宽的匹配往往需要复杂的技术和高昂的成本,奎芯科技通过这种匹配,降低了技术难度和成本,提供了更具竞争力的解决方案。

【“分离”,突破COWOS先进制造封锁】

CoWoS(Chip-on-Wafer-on-Substrate)是一种高端封装技术,常用于将多个芯片集成到一个封装中,通常是高带宽内存(HBM)和处理器之间的连接。由于CoWoS能够实现非常高的数据传输带宽,因此它通常与HBM(如HBM3)搭配使用,特别是在高性能计算(HPC)和人工智能(AI)领域中,因为这些应用需要大量的内存带宽。

然而,受到CoWoS和HBM3的技术限制和产能带来的约束,主要来自于流片和生产环节。奎芯的ML100 IO Die,在支持UCIe接口的基础上,将主芯片和IO die分开,让它们不再受限于封装技术和内存类型的选择。主芯片可以根据不同的应用需求,选择不同类型的内存(如LPDDR或HBM)。

客户可以将LPDDR作为内存接口,而不是依赖HBM。这样做的好处是,LPDDR不受出口限制,也可以避免使用高端的CoWoS封装技术,从而实现了技术上的灵活性。

这种“分离”的技术方案,并不是指完全放弃高端技术,而是通过采用更灵活、受限程度较低的技术方案,减低对高端技术的依赖。

【“分离”,提高设计方案的应用灵活度】

除了在供应链上的意义外,这种IO die和主芯片分离的设计,也具有技术层面的意义,同时也为芯片公司提供了更多的市场适应性和技术灵活性。

首先,“分离”后主芯片和HBM之间不再存在边界上的尺寸制约,所以可以连接更多的IO Die和HBM颗粒。

其次分离之后后的主芯片设计不需要受到内存类型、封装大小等方面的限制,也能根据市场需求切换不同内存解决方案。例如原本的设计是基于HBM的应用于训练场景的AI芯片,如果需要切换到推理的场景,可以直接用ML100的方案将HBM切换LPDDR的灵活接入,而不需要重新设计整个主芯片或进行复杂的封装。

“因为LPDDR现在在推演的领域用得比较多,如果这块儿主芯片,不推向训练市场,而是推向推演市场,主芯片不需要重新流片的,只要换个IO Die就可以变成高性能的推演芯片了。”唐睿分享到。

据悉,奎芯科技的ML100 IO Die产品已经在今年完成了两个商业化应用(商业闭环),并且成功获得了两个客户的支持或订单,表明该产品在市场上已经获得了一定的认可。

在国内Chiplet变局中捕捉机遇,发挥互联IP产品独特价值

UCIe标准自2022年推出以来,在业界引起了广泛关注。许多业内人士认为这是近年来最为重要的标准之一,尤其是在硅谷的讨论中,UCIe的发布被认为是一个突破性的进展。然而,尽管这一标准已经推出了两三年,但实际上它并没有完全达到预期的效果。不同IP公司之间的互联互通仍然是一个巨大的挑战,这既是机遇也是挑战。从机遇的角度看,已经采用UCIe IP的公司在自家芯片上集成这些标准,可以帮助他们形成闭环生态系统,但对于整个行业来说,特别是对于小公司而言,这种绑定可能会限制更广泛的开放生态。

在UCIe演进的过程中,尽管很多公司都在致力于解决不同层次之间的互联互通问题,但目前的情况仍然让产业界的互联互通面临困难。奎芯科技正通过技术创新努力克服这一挑战,特别是在先发优势方面占据一定的优势。目前奎芯科技在多个关键节点上已经完成了16G和32G两个速度标准的UCIe IP设计,并在标准封装上实现了这些速率。相较于先进封装技术,标准封装的信道质量较差,因此在同样的速率下,标准封装实现的难度更大。这种技术突破进一步展示了国内厂商在UCIe标准领域的创新能力。

在国产化的过程中,真正的突破并不是简单的替换国外技术,而是通过创新来创造新的价值。“首先还是要找到一个自己产品的定位,这种就是简单的replacement、一个替换是做不到的,你一定要在变局中带来一个价值。”唐睿坦言到。

尤其在面临行业变局时,找到合适的技术路径和产品定位至关重要。对于国内公司来说,Chiplet技术为国产化提供了一个新的机会。在当前摩尔定律逐渐受到制约的背景下,Chiplet技术通过模块化设计能够在7纳米至12纳米制程下实现功能的叠加、算力的突破和异构集成,成为一种有效的解决方案。与国外公司相比,国内的制程受到一定限制,但这也为国内公司提供了创新的空间,可以在其他技术路径上实现突破,而不是依赖高端的3纳米、5纳米制程。

唐睿表示,奎芯科技在UCIe IP上的完整性构成了其重要的技术优势。客户选择奎芯的Chiplet IO die后,不仅能够实现主芯片与UCIe IP的同质芯片互联,还能通过奎芯的IO die进行接口转换,从而为客户的设计提供更大的灵活性。此外,奎芯还提供配套的Chiplet产品,这进一步增强了其竞争优势。

应用发展、技术趋势和时代机遇交融,未来可期

“大的产业格局看,我们在三个交叉赛道上都属于早期阶段,一个是AI对芯片的要求,第二是Chiplet的发展,还有全面芯片国产化,这三点都处于早期。”唐睿分享到。

这三大机遇相互交织,形成了中国芯片产业发展的独特动力。AI技术的推动促进了对高性能芯片的需求,而Chiplet技术则为国内芯片企业提供了突破的技术路径,解决了制程技术瓶颈。与此同时,芯片国产化的战略目标迫切要求国内企业加速技术积累和自主创新,确保在全球产业链中的话语权。三者的融合,不仅为中国半导体产业带来了前所未有的创新机会,也为产业链的独立性和安全性奠定了基础。

“所以我们继续打磨好自己的产品,未来可期。”唐睿充满信心。