在现代FPGA设计中,数据传输速度日益提升,特别是在千兆网、高速串行接口和DDR内存接口等应用中,数据传输速率的要求尤为严格。为了应对这一挑战,Xilinx FPGA引入了IDDR(Input Double Data Rate)和ODDR(Output Double Data Rate)原语,以支持双倍数据速率(DDR)的传输。本文将详细介绍VIVADO中IDDR与ODDR原语的使用,并附上相关代码示例。

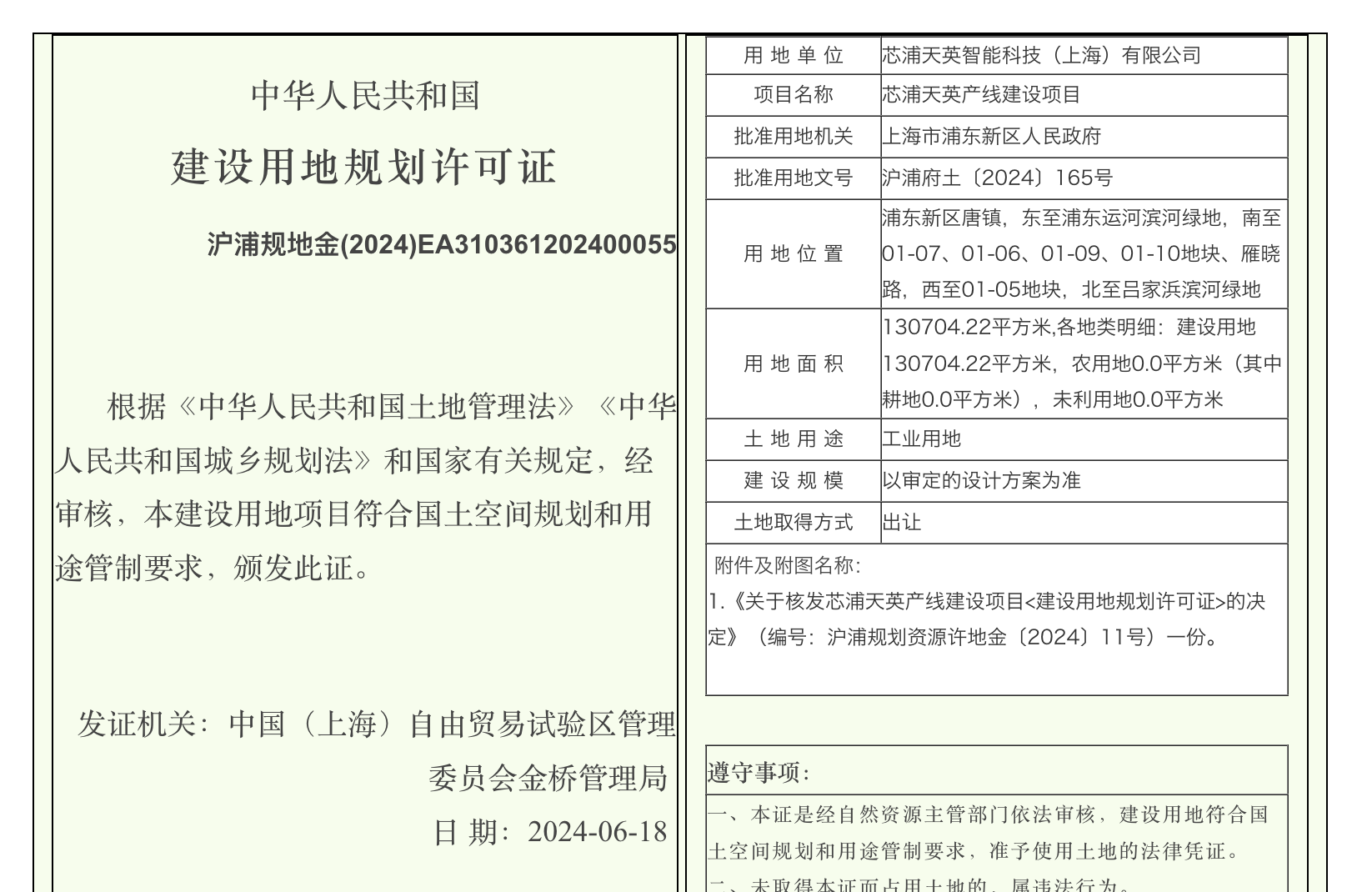

IDDR原语详解

IDDR(输入双数据速率)原语主要用于接收数据,它能够在每个时钟边沿捕获数据,从而实现双倍数据速率的数据传输。这在FPGA设计中尤为重要,当外部数据源的速率高于内部处理速度时,IDDR可以有效地提高数据吞吐率。

IDDR原语的基本结构包括时钟输入、数据输入、使能信号、复位信号和输出信号等。其中,时钟输入用于同步数据的捕获,数据输入则是接收的外部数据,使能信号用于控制原语的启动,复位信号用于重置原语的状态,输出信号则是捕获的数据。

IDDR原语有多种工作模式,其中最常见的是“OPPOSITE_EDGE”模式。在此模式下,一个时钟的上升沿与下降沿数据正好可以在下一个时钟上升沿的两个输出端口Q1和Q2上被捕获。这种模式的时序关系清晰,适用于大多数应用。

以下是一个IDDR原语的Verilog代码示例:

verilog

IDDR#(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // 时钟边沿配置

.INIT_Q1(1'b0), // Q1初始值

.INIT_Q2(1'b0), // Q2初始值

.SRTYPE("SYNC") // 置位/复位类型

) IDDR_ctrl (

.Q1(data_en), // 正时钟边沿数据输出

.Q2(data_err), // 负时钟边沿数据输出

.C(rx_clk), // 时钟输入

.CE(1'b1), // 时钟使能

.D(rx_ctrl), // DDR数据输入

.R(~rst_n), // 复位信号

.S(1'b0) // 置位信号

);

ODDR原语详解

ODDR(输出双数据速率)原语则用于产生双倍数据速率的输出信号。与IDDR类似,ODDR在每个时钟边沿都可以驱动数据,提高了输出数据的速率。ODDR在设计时需要特别关注数据的输出时序和时钟的相位关系,以确保在正确的时间点上提供有效的数据。

ODDR原语的基本结构与IDDR类似,包括时钟输入、数据输入、使能信号、复位信号和输出信号等。不同之处在于,ODDR有两个数据输入端口D1和D2,分别对应于时钟的正边沿和负边沿。

ODDR原语同样有多种工作模式,其中最常见的是“OPPOSITE_EDGE”模式。在此模式下,两个数据输入端口D1和D2的数据会被合成到一个时钟周期内,分别在时钟的正边沿和负边沿输出。

以下是一个ODDR原语的Verilog代码示例:

verilog

ODDR#(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // 时钟边沿配置

.INIT(1'b0), // 初始值

.SRTYPE("SYNC") // 置位/复位类型

) ODDR_ctrl (

.Q(tx_data_ctrl), // DDR输出

.C(gb_tx_clk), // 时钟输入

.CE(1'b1), // 时钟使能

.D1(gb_tx_data_en), // 正时钟边沿数据输入

.D2(gb_tx_data_err), // 负时钟边沿数据输入

.R(~rst_n), // 复位信号

.S(1'b0) // 置位信号

);

总结

IDDR和ODDR原语是Xilinx FPGA设计中实现高速数据传输的关键组件。IDDR用于接收双倍数据速率的数据,提高了数据吞吐率;而ODDR则用于产生双倍数据速率的输出信号,提高了数据传输效率。通过合理配置IDDR和ODDR的参数,并编写相应的Verilog代码,可以实现高效、可靠的FPGA设计。

在实际应用中,IDDR和ODDR原语的使用需要结合具体的应用场景进行参数配置和时序分析。VIVADO设计环境提供了强大的工具和IP核库,帮助用户快速集成和调试这些原语,以实现高效且可靠的FPGA设计。

理解和熟练运用IDDR和ODDR原语,对于进行高效、高质量的FPGA设计至关重要。通过合理利用这些原语,可以设计出更加灵活、高速的数字系统,满足现代数字通信和数据处理的高要求。