在高速串行通信中,集成误码率测试仪(Integrated Bit Error Ratio Tester,简称IBERT)是Xilinx提供的一款用于测试transceiver的免费IP。IBERT的example design集成了transceiver、logic、ILA、VIO、Pattern Generator and Checker、DRP等功能,为用户提供了一个便捷的测试平台,无需编写复杂的代码即可验证当前硬件条件下transceiver能否在用户需要的线速率下正常工作。

IBERT的功能与特点

IBERT的核心功能是通过误码率测试来评估FPGA中GTX(Gigabit Transceiver)的通断和通信性能。一般的误码率可以低至10^-12级别,这为用户提供了高精度的测试结果。IBERT通过FPGA内部资源,能够生成伪随机二进制序列(PRBS),如PRBS7、PRBS9、PRBS15等,用于测试高速串行通道传输的误码率。这些PRBS数据类型的选择主要基于其游程(Run Length)不同,从而影响Pattern Dependent Jitter(PDJ)。

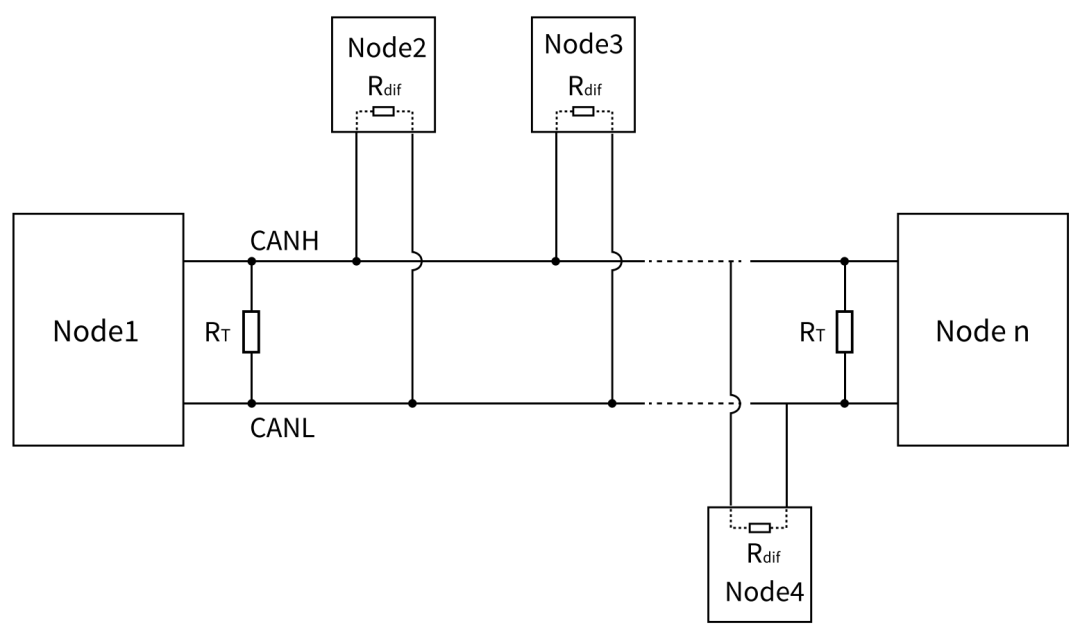

IBERT还提供了多种环回模式,包括Near-end PCS环回、Near-end PMA环回、Far-end PMA环回和Far-end PCS环回。这些模式允许用户在内部或外部进行自回环测试,从而验证transceiver的不同部分是否工作正常。例如,Near-end PCS环回测试的是FPGA内部物理编码子层(PCS)的功能,而Far-end PMA环回则测试了包括传输线在内的完整链路。

IBERT的使用步骤

使用IBERT进行测试通常包括以下几个步骤:

IP核生成与配置:

在Vivado中,通过IP catalog搜索IBERT,并进行定制。在配置过程中,需要选择系统时钟源,可以选择外部时钟源或由GTX差分时钟提供。此外,还需要配置参考时钟(Refclk),其驱动能力范围需参考具体器件系列的transceiver文档。

生成Bitstream并下载:

配置完成后,生成Bitstream文件,并将其下载到FPGA芯片中。

创建Link并配置参数:

通过JTAG接口将Bitstream下载到FPGA后,点击Auto detect links或create links,创建link链接。用户可以配置link中的参数,如PRBS模式、环回模式、TX差分摆幅(TX diff-swing)、TX预加重(TX Pre-Emphasis)等。

观察测试结果:

在配置完成后,通过观察GTX通道的Status和误码率,可以评估transceiver的性能。IBERT还提供了Eye Scan功能,用于扫描眼图,以评估信号的质量。用户可以选择2D Full Eye或1D Bathtub扫描类型,以及不同的误码率(BER)目标,如10^-9,来兼顾扫描时间和可靠度。

常见问题与解决方案

在使用IBERT进行测试时,可能会遇到一些问题,如测试不通过或Near-end环回测试失败。这时,首先需要检查时钟质量和电源质量。时钟和电源的要求在每个系列的transceiver文档和data and switching文档上都有详细描述。电源测试时,需要选择靠近FPGA芯片的测试点,并测试真实负载下的电源。此外,手册上要求的电源最大电压值和最小电压值需考虑纹波和噪声的影响。

如果测试的对端器件不是FPGA,而是其他芯片(如DSP、专用芯片、Switch等),则需要查阅对端芯片的资料,看其是否支持类似的环回模式。如果支持,FPGA这一侧可以将loopback mode设置为none,对端芯片设置为相应的环回模式,从而测试完整链路。如果不支持,则需要在硬件环境上做环回,如使用接插件、耦合电容等。

结论

IBERT作为Xilinx提供的一款强大的测试工具,为FPGA中的高速串行通信测试提供了极大的便利。通过误码率测试和眼图扫描,用户可以准确评估transceiver的性能,从而确保高速串行设计调试的顺利进行。无论是内部自回环还是外部自回环,IBERT都能提供全面的测试解决方案,帮助用户快速定位并解决问题。